## LMH2180 75 MHz Dual Clock Buffer

## **General Description**

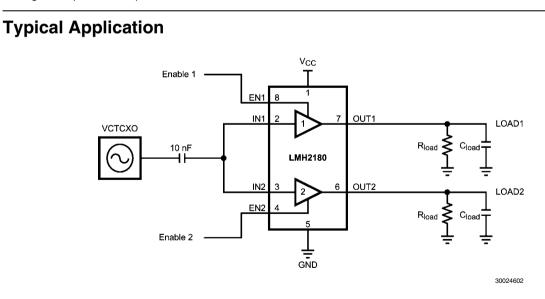

The LMH2180 is a high speed dual clock buffer designed for portable communications and applications requiring multiple accurate multi-clock systems. The LMH2180 integrates two 75 MHz low noise buffers with independent shutdown pins into a small package. The LMH2180 ensures superb system operation between the baseband and the oscillator signal path by eliminating crosstalk between the multiple clock signals.

Unique technology and design provides the LMH2180 with the ability to accurately drive both large capacitive and resistive loads. Low supply current combined with shutdown pins for each channel means the LMH2180 is ideal for battery powered applications. This part does not use an internal ground reference, thus providing additional system flexibility.

The flexible buffers provide system designers the capacity to manage complex clock signals in the latest wireless applications. Each buffer delivers 106 V/us internal slew rate with independent shutdown and duty cycle precision. Each input is internally biased to 1V, removing the need for external resistors. Both channels have rail-to-rail inputs and outputs, a gain of one, and are AC coupled with the use of one capacitor.

Replacing a discrete buffer solution with the LMH2180 provides many benefits: simplified board layout, minimized parasitic components, simplified BOM, design durability across multiple applications, simplification of clock paths, and the ability to reduce the number of clock signal generators in the system. The LMH2180 is produced in the tiny packages minimizing the required PCB space.

## Features

(Typical values are:  $V_{SUPPLY} = 2.7V$  and  $C_L = 10$  pF, unless otherwise specified.)

- Small signal bandwidth 78 MHz

- -2.4V to 5V Supply voltage range -123 dBc/Hz

- Phase noise ( $V_{IN} = 1 V_{PP}$ ,  $f_{\rm C} = 38.4$  MHz,  $\Delta f = 1$  kHz)

- Slew rate

- -

- Total supply current Shutdown current

- Rail-to-rail input and output

- -Individual buffer enable pins

- Rapid Ton technology

- Crosstalk rejection circuitry -

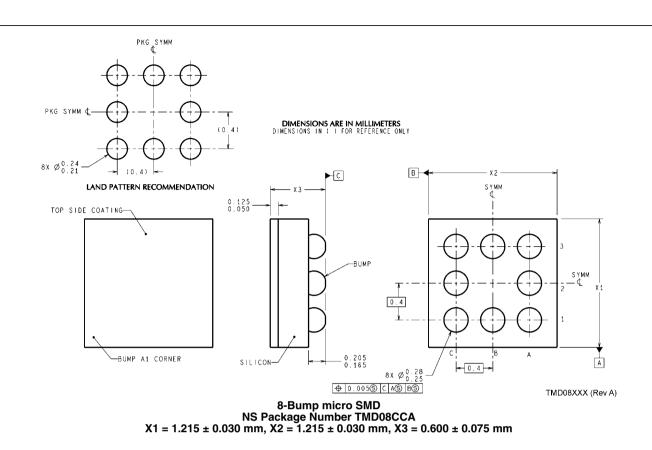

— 8-Bump micro SMD

-Packages:

- 8-Pin LLP, Solder Bump and no Pullback

- Temperature range Applications

- 3G mobile applications

- WLAN-WiMAX modules

- TD SCDMA multi-mode MP3 and camera

- **GSM** modules

- Oscillator modules

-40°C to 85°C

106 V/µs

2.3 mA

30 µA

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltages (V+ – V-) | 5.5V           |

|---------------------------|----------------|

| ESD Tolerance             |                |

| Human Body (Note 4)       | 2000V          |

| Machine Model (Note 5)    | 200V           |

| Charged Device Model      | 1000V          |

| Storage Temperature Range | –65°C to 150°C |

## **2.7V Electrical Characteristics**

Junction Temperature (Note 3)150°CSoldering Information150°CInfrared or Convection (35 sec.)235°COperating Ratings (Note 1)

| Supply Voltage (V+ – V-)                | 2.4V to 5.0V                      |

|-----------------------------------------|-----------------------------------|

| Temperature Range (Notes 2, 3)          | $-40^{\circ}$ C to $85^{\circ}$ C |

| Package Thermal Resistance (Notes 2, 3) |                                   |

| 8-Pin LLP (θ <sub>JA</sub> )            | 217°C/W                           |

| 8-Bump micro SMD (θ <sub>JA</sub> )     | 90°C/W                            |

|                                         |                                   |

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}$ C,  $V_{DD} = 2.7$ V,  $V_{SS} = 0$ V,  $V_{CM} = 1$ V, Enable<sub>1,2</sub> =  $V_{DD}$ ,  $C_L = 10$  pF,  $R_L = 30$  k $\Omega$ , Load is connected to  $V_{SS}$ ,  $C_{COUPLING} = 10$  nF. **Boldface** limits apply at temperature range extremes of operating condition. See (Note 2)

| Symbol                | Parameter                                                 | Conditions                                                               | Min<br>(Note 7) | Typ<br>(Note 6) | Max<br>(Note 7)                       | Units  |

|-----------------------|-----------------------------------------------------------|--------------------------------------------------------------------------|-----------------|-----------------|---------------------------------------|--------|

| Frequency             | y Domain Response                                         |                                                                          | ( )             | ,               | , , , , , , , , , , , , , , , , , , , |        |

| SSBW                  | Small Signal Bandwidth                                    | V <sub>IN</sub> = 100 mV <sub>PP</sub> ; -3 dB                           |                 | 78              |                                       | MHz    |

| LSBW                  | Large Signal Bandwidth                                    | V <sub>IN</sub> = 1.0 V <sub>PP</sub> ; -3 dB                            |                 | 60              |                                       | MHz    |

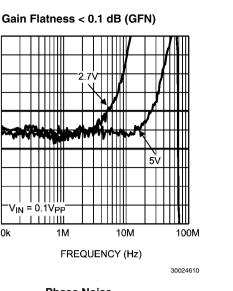

| GFN                   | Gain Flatness < 0.1 dB                                    | f > 100 kHz                                                              |                 | 4.9             |                                       | MHz    |

| Distortion            | and Noise Performance                                     |                                                                          |                 |                 |                                       |        |

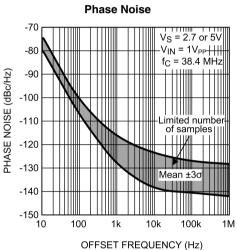

| φ <sub>n</sub>        | Phase Noise                                               | $V_{IN}$ = 1 $V_{PP}$ , $f_C$ = 38.4 MHz, $\Delta f$ = 1 kHz             |                 | -123            |                                       | dBc/Hz |

|                       |                                                           | $V_{IN} = 1 V_{PP}, f_{C} = 38.4 \text{ MHz}, \Delta f = 10 \text{ kHz}$ |                 | -132            |                                       | dBc/Hz |

| e <sub>n</sub>        | Input-Referred Voltage Noise                              | $f = 1 \text{ MHz}, R_{\text{SOURCE}} = 50\Omega$                        |                 | 13              |                                       | nV/√Hz |

| I <sub>SOLATION</sub> | Output to Input                                           | $f = 1 MHz, R_{SOURCE} = 50\Omega$                                       |                 | 84              |                                       | dB     |

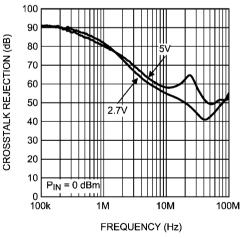

| СТ                    | Crosstalk Rejection                                       | $f = 38.4 \text{ MHz}, V_{IN} = 1 V_{PP}$                                |                 | 41              |                                       | dB     |

| Time Dom              | ain Response                                              |                                                                          |                 |                 |                                       |        |

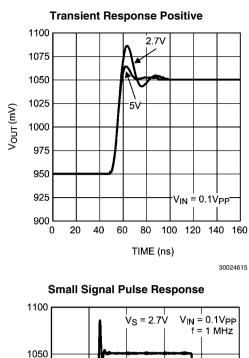

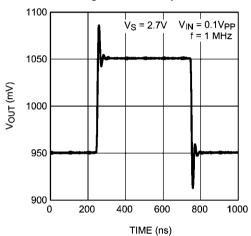

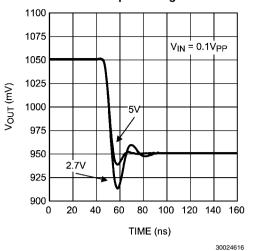

| t <sub>r</sub>        | Rise Time     0.1 V <sub>PP</sub> Step (10-90%)           |                                                                          |                 | 6               |                                       | ns     |

| t <sub>f</sub>        | Fall Time                                                 |                                                                          |                 | 5               |                                       | ns     |

| t <sub>s</sub>        | Settling Time to 0.1%                                     | 1 V <sub>PP</sub> Step                                                   |                 | 120             |                                       | ns     |

| OS                    | Overshoot                                                 | 0.1 V <sub>PP</sub> Step                                                 |                 | 37              |                                       | %      |

| SR                    | Slew Rate (Note 8)                                        | V <sub>IN</sub> = 2 V <sub>PP</sub>                                      |                 | 106             |                                       | V/µs   |

| Static DC             | Performance                                               |                                                                          |                 |                 |                                       |        |

| I <sub>S</sub>        | Supply Current                                            | Enable <sub>1,2</sub> = V <sub>DD</sub> ; No Load                        |                 | 2.3             | 2.7<br><b>2.9</b>                     | mA     |

|                       |                                                           | $Enable_1 = V_{DD}$ , $Enable_2 = V_{SS}$ , No Load                      |                 | 1.3             | 1.5<br><b>1.6</b>                     | mA     |

|                       |                                                           | Enable <sub>1,2</sub> = V <sub>SS</sub> ; No Load                        |                 | 30              | 41<br><b>46</b>                       | μA     |

| PSRR                  | Power Supply Rejection Ratio                              | DC (3.0V to 5.0V)                                                        | 65<br><b>64</b> | 68              |                                       | dB     |

| A <sub>CL</sub>       | Small Signal Voltage Gain                                 | V <sub>IN</sub> = 0.2 V <sub>PP</sub>                                    | 0.95            | 1.0             | 1.05                                  | V/V    |

| V <sub>OS</sub>       | Output Offset Voltage                                     |                                                                          |                 | -0.5            | 17<br><b>18</b>                       | mV     |

| TC V <sub>OS</sub>    | Temperature Coefficient Output<br>Offset Voltage (Note 9) |                                                                          |                 | 2.8             |                                       | µV/∘C  |

| R <sub>OUT</sub>      | Output Resistance                                         | f = 100 kHz                                                              |                 | 0.6             |                                       | 0      |

|                       |                                                           | f = 38.4 MHz                                                             |                 | 166             |                                       | Ω      |

| Symbol               | Parameter                                      | Conditions                                       | Min<br>(Note 7)     | Typ<br>(Note 6) | Max<br>(Note 7) | Units |

|----------------------|------------------------------------------------|--------------------------------------------------|---------------------|-----------------|-----------------|-------|

| Miscellane           | eous Performance                               |                                                  |                     | •               |                 |       |

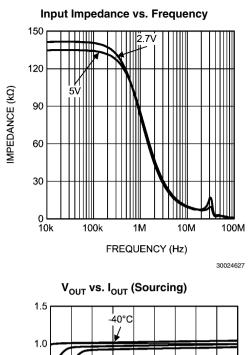

| R <sub>IN</sub>      | Input Resistance per Buffer                    | Enable = $V_{DD}$                                |                     | 137             |                 | ko    |

|                      |                                                | Enable = V <sub>SS</sub>                         |                     | 137             |                 | kΩ    |

| C <sub>IN</sub>      | Input Capacitance per Buffer                   | Enable = $V_{DD}$                                |                     | 1.3             |                 | ъĘ    |

|                      |                                                | Enable = V <sub>SS</sub>                         |                     | 1.3             |                 | pF    |

| Z <sub>IN</sub>      | Input Impedance                                | f = 38.4 MHz, Enable = V <sub>DD</sub>           |                     | 4.5             |                 | kΩ    |

|                      |                                                | f = 38.4 MHz, Enable = V <sub>SS</sub>           |                     | 4.2             |                 |       |

| Vo                   | Output Swing Positive                          | $V_{IN} = V_{DD}$                                | 2.66<br><b>2.65</b> | 2.69            |                 | V     |

|                      | Output Swing Negative                          | V <sub>IN</sub> = V <sub>SS</sub>                |                     | 19              | 35<br><b>37</b> | mV    |

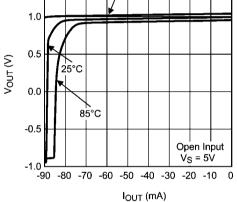

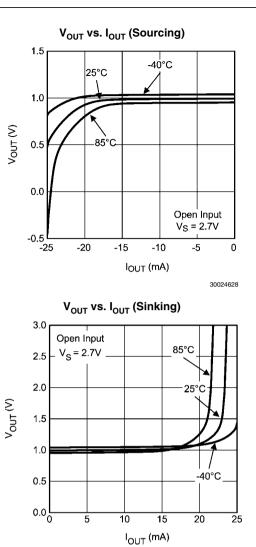

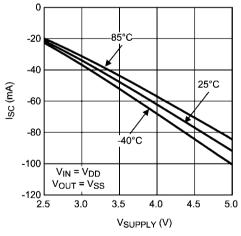

| I <sub>SC</sub>      | Output Short-Circuit Current<br>(Notes 10, 11) | Sourcing, $V_{IN} = V_{DD}$ , $V_{OUT} = V_{SS}$ | -21<br><b>-18</b>   | -25             |                 |       |

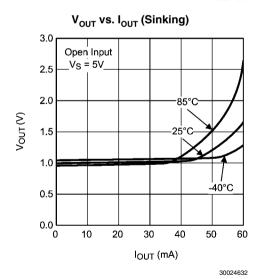

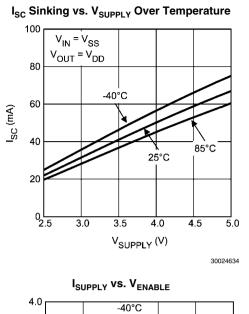

|                      |                                                | Sinking, $V_{IN} = V_{SS}$ , $V_{OUT} = V_{DD}$  | 23<br>15            | 25              |                 | mA    |

| V <sub>en_hmin</sub> | Enable High Active Minimum Voltage 1.2         |                                                  |                     |                 |                 |       |

| V <sub>en_Imax</sub> | Enable Low Inactive Maximum<br>Voltage         |                                                  |                     | 0.6             |                 | V     |

## **5V Electrical Characteristics**

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}$ C,  $V_{DD} = 5$ V,  $V_{SS} = 0$ V,  $V_{CM} = 1$ V, Enable<sub>1,2</sub> =  $V_{DD}$ ,  $C_L = 10$  pF,  $R_L = 30$  k $\Omega$ , Load is connected to  $V_{SS}$ ,  $C_{COUPLING} = 10$  nF. **Boldface** limits apply at temperature range extremes of operating condition. See (Note 2)

| Symbol                | Parameter                    | Conditions                                                               | Min      | Тур      | Max               | Units  |

|-----------------------|------------------------------|--------------------------------------------------------------------------|----------|----------|-------------------|--------|

|                       |                              |                                                                          | (Note 7) | (Note 6) | (Note 7)          |        |

|                       | Domain Response              |                                                                          |          |          |                   |        |

| SSBW                  | Small Signal Bandwidth       | V <sub>IN</sub> = 100 mV <sub>PP</sub> ; –3 dB                           |          | 87       |                   | MHz    |

| LSBW                  | Large Signal Bandwidth       | $V_{IN} = 1.0 V_{PP}; -3 \text{ dB}$                                     |          | 68       |                   | MHz    |

| GFN                   | Gain Flatness < 0.1 dB       | f > 100 kHz                                                              |          | 25       |                   | MHz    |

| Distortion            | and Noise Performance        |                                                                          |          |          |                   |        |

| φ <sub>n</sub>        | Phase Noise                  | $V_{IN}$ = 1 $V_{PP}$ , $f_C$ = 38.4 MHz, $\Delta f$ = 1 kHz             |          | -123     |                   | dBc/Hz |

|                       |                              | $V_{IN} = 1 V_{PP}, f_{C} = 38.4 \text{ MHz}, \Delta f = 10 \text{ kHz}$ |          | -132     |                   | dBc/Hz |

| e <sub>n</sub>        | Input-Referred Voltage Noise | $f = 1 \text{ MHz}, R_{SOURCE} = 50\Omega$                               |          | 12       |                   | nV/√Hz |

| I <sub>SOLATION</sub> | Output to Input              | $f = 1 \text{ MHz}, R_{SOURCE} = 50\Omega$                               |          | 84       |                   | dB     |

| СТ                    | Crosstalk Rejection          | f = 38.4 MHz, P <sub>IN</sub> = 0 dBm                                    |          | 59       |                   | dB     |

| Time Dom              | ain Response                 | •                                                                        |          |          |                   |        |

| t <sub>r</sub>        | Rise Time                    | 0.1 V <sub>PP</sub> Step (10-90%)                                        |          | 6        |                   | ns     |

| t <sub>f</sub>        | Fall Time                    |                                                                          |          | 6        |                   | ns     |

| t <sub>s</sub>        | Settling Time to 0.1%        | 1 V <sub>PP</sub> Step                                                   |          | 70       |                   | ns     |

| OS                    | Overshoot                    | 0.1V <sub>PP</sub> Step                                                  |          | 13       |                   | %      |

| SR                    | Slew Rate (Note 8)           | V <sub>IN</sub> = 2 V <sub>PP</sub>                                      |          | 124      |                   | V/µs   |

| Static DC             | Performance                  |                                                                          |          |          |                   |        |

| I <sub>S</sub>        | Supply Current               | Enable <sub>1,2</sub> = V <sub>DD</sub> ; No Load                        |          | 3.4      | 4.0<br><b>4.1</b> | mA     |

|                       |                              | $Enable_1 = V_{DD}$ , $Enable_2 = V_{SS}$ ; No<br>Load                   |          | 1.8      | 2.2<br><b>2.3</b> | mA     |

|                       |                              | Enable <sub>1,2</sub> = V <sub>SS</sub> ; No Load                        |          | 32       | 43<br><b>49</b>   | μA     |

www.national.com

\_\_\_\_\_

LMH2180

| 0 |

|---|

| õ |

| - |

| ณ |

| Т |

| 5 |

| 5 |

| Symbol               | Parameter                                                 | Conditions                                       | Min<br>(Note 7)     | Typ<br>(Note 6) | Max<br>(Note 7) | Units |  |

|----------------------|-----------------------------------------------------------|--------------------------------------------------|---------------------|-----------------|-----------------|-------|--|

| PSRR                 | Power Supply Rejection Ratio                              | DC (3.0V to 5.0V)                                | 65<br><b>64</b>     | 68              |                 | dB    |  |

| A <sub>CL</sub>      | Small Signal Voltage Gain                                 | $V_{IN} = 0.2 V_{PP}$                            | 0.95                | 1.0             | 1.05            | V/V   |  |

| V <sub>OS</sub>      | Output Offset Voltage                                     |                                                  |                     | -1.4            | 21<br><b>22</b> | mV    |  |

| TC V <sub>OS</sub>   | Temperature Coefficient Output<br>Offset Voltage (Note 9) |                                                  |                     | 2.4             |                 | µV/°C |  |

| R <sub>OUT</sub>     | Output Resistance                                         | f = 100 kHz                                      |                     | 0.5             |                 |       |  |

|                      |                                                           | f = 38.4 MHz                                     |                     | 126             |                 | Ω     |  |

| Miscellane           | eous Performance                                          |                                                  |                     |                 |                 |       |  |

| R <sub>IN</sub>      | Input Resistance per Buffer                               | Enable = $V_{DD}$                                |                     | 138             |                 |       |  |

|                      |                                                           | Enable = V <sub>SS</sub>                         |                     | 138             |                 | kΩ    |  |

| C <sub>IN</sub>      | Input Capacitance per Buffer                              | Enable = $V_{DD}$                                |                     | 1.3             |                 |       |  |

|                      |                                                           | Enable = V <sub>SS</sub>                         |                     | 1.3             |                 | pF    |  |

| Z <sub>IN</sub>      | Input Impedance                                           | f = 38.4 MHz, Enable = $V_{DD}$                  |                     | 4.3             |                 |       |  |

|                      |                                                           | f = 38.4 MHz, Enable = V <sub>SS</sub>           |                     | 4.2             |                 | kΩ    |  |

| V <sub>o</sub>       | Output Swing Positive                                     | V <sub>IN</sub> = V <sub>DD</sub>                | 4.96<br><b>4.95</b> | 4.99            |                 | V     |  |

|                      | Output Swing Negative                                     | $V_{IN} = V_{SS}$                                |                     | 10              | 35<br><b>50</b> | mV    |  |

| I <sub>sc</sub>      | Output Short-Circuit Current<br>(Notes 10, 11)            | Sourcing, $V_{IN} = V_{DD}$ , $V_{OUT} = V_{SS}$ | -80<br>- <b>62</b>  | -90             |                 | mA    |  |

|                      |                                                           | Sinking, $V_{IN} = V_{SS}$ , $V_{OUT} = V_{DD}$  | 60<br><b>43</b>     | 65              |                 | mA    |  |

| V <sub>en_hmin</sub> | Enable High Active Minimum Voltage                        |                                                  |                     | 1.2             |                 |       |  |

| V <sub>en_Imax</sub> | Enable Low Inactive Maximum Voltage                       |                                                  |                     | 0.6             |                 | V     |  |

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of the device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

Note 2: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in the *Absolute Maximum Ratings*, whichever is lower.

Note 4: Human body model, applicable std. JESD22-A114C.

Note 5: Machine model, applicable std. JESD22-A115-A.

Note 6: Typical values represent the most likely parametric norms at  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 7: Datasheet min/max specification limits are guaranteed by test or statistical analysis.

Note 8: Slew rate is the average of the rising and falling slew rates.

Note 9: Average Temperature Coefficient is determined by dividing the changing in a parameter at temperature extremes by the total temperature change. Note 10: Short–Circuit test is a momentary test. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

Note 11: Positive current corresponds to current flowing into the device.

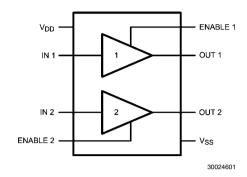

## **Block Diagram**

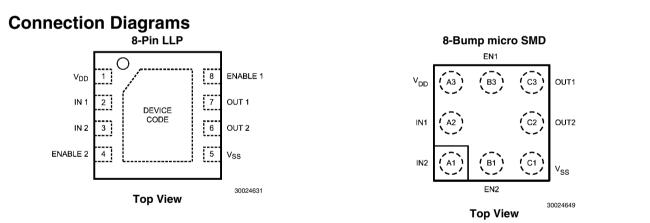

## **Pin Descriptions**

| Pin No.<br>LLP | Pin No.<br>microSMD | Pin Name        | Description               |  |

|----------------|---------------------|-----------------|---------------------------|--|

| 1              | A3                  | V <sub>DD</sub> | Voltage supply connection |  |

| 2              | A2                  | IN 1            | Input 1                   |  |

| 3              | A1                  | IN 2            | Input 2                   |  |

| 4              | B1                  | ENABLE 2        | Enable buffer 2           |  |

| 5              | C1                  | V <sub>SS</sub> | Ground connection         |  |

| 6              | C2                  | OUT 2           | Output 2                  |  |

| 7              | C3                  | OUT 1           | Output 1                  |  |

| 8              | B3                  | ENABLE 1        | Enable buffer 1           |  |

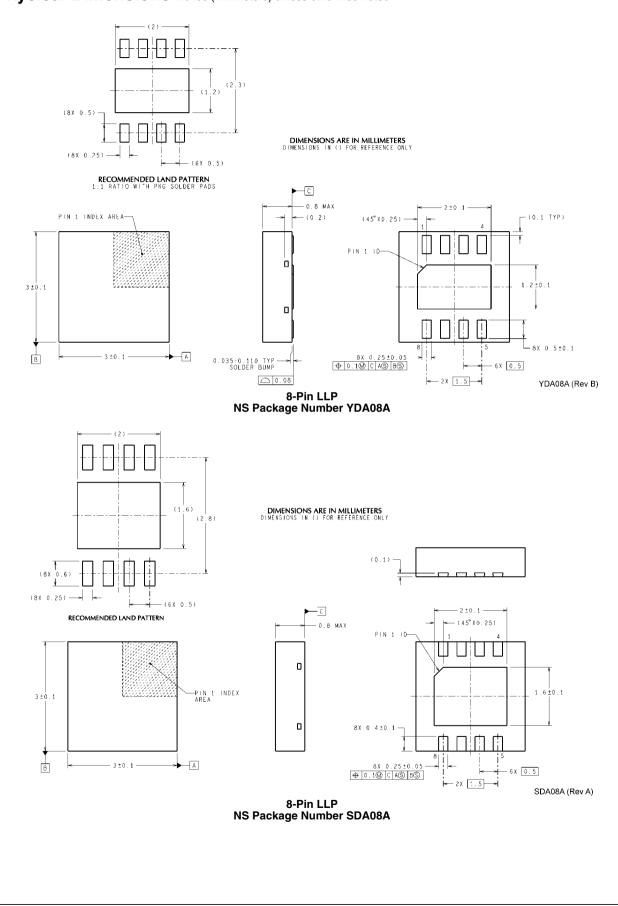

## **Ordering Information**

| Package                  | Part Number | Package Marking | Transport Media          | NSC Drawing |

|--------------------------|-------------|-----------------|--------------------------|-------------|

| 8-Pin LLP                | LMH2180YD   | 2180Y           | 1k Units Tape and Reel   | YDA08A      |

| Solder Bump              | LMH2180YDX  | 21001           | 4.5k Units Tape and Reel | T DAUGA     |

|                          | LMH2180SD   |                 | 1k Units Tape and Reel   |             |

| 8-Pin LLP<br>No Pullback | LMH2180SDE  | 2180S           | 250 Units Tape and Reel  | SDA08A      |

|                          | LMH2180SDX  |                 | 4.5k Units Tape and Reel |             |

| 8-Bump micro SMD         | LMH2180TM   |                 | 250 Units Tape and Reel  | TMD08CCA    |

|                          | LMH2180TMX  | CA              | 3k Units Tape and Reel   | TWIDUOCCA   |

30024603

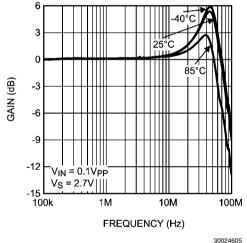

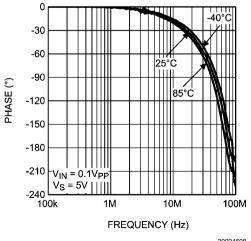

**Phase Response Over Temperature**

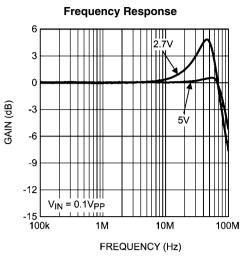

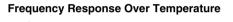

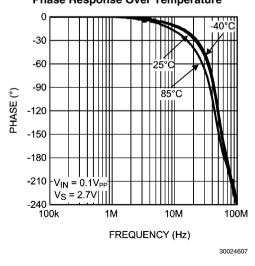

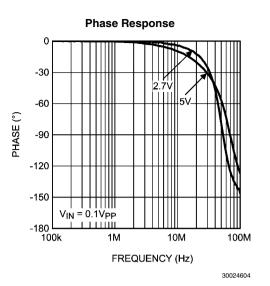

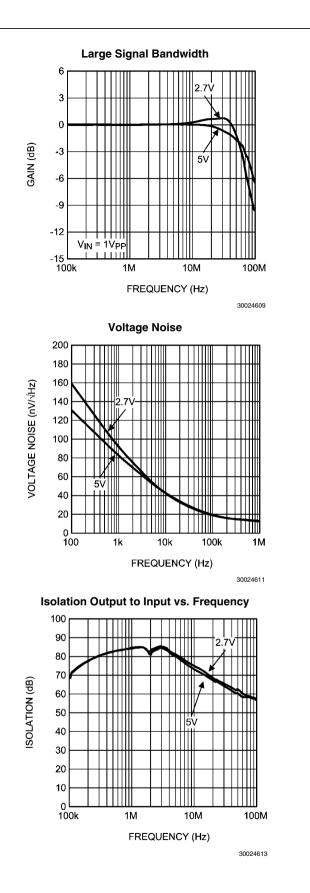

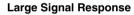

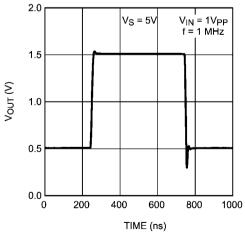

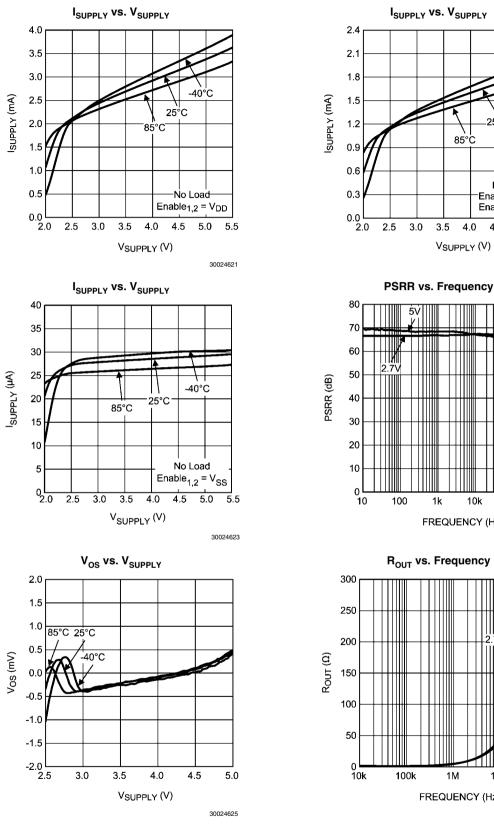

**Typical Performance Characteristics**  $T_A = 25^{\circ}C$ ,  $V_{DD} = 2.7V$ ,  $V_{SS} = 0V$ ,  $Enable_{1,2} = V_{DD}$ ,  $C_L = 10 \text{ pF}$ ,  $R_L = 30 \text{ k}\Omega$  and  $C_{COUPLING} = 10 \text{ nF}$ , unless otherwise specified.

Frequency Response Over Temperature

**Phase Response Over Temperature**

30024608

LMH2180

0.5

0.4

0.3

0.2 0.1

0

-0.1

-0.2

-0.3

-0.4

-0.5 – 100k

[17

1M

V<sub>IN</sub> = 0.1V<sub>PF</sub>

NORMALIZED GAIN (dB)

30024612

**Crosstalk Rejection vs. Frequency**

**Transient Response Negative**

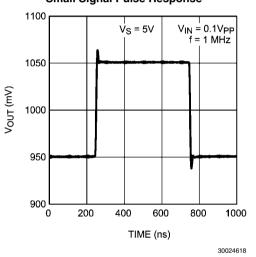

Small Signal Pulse Response

100 1k 10k 100k 1M FREQUENCY (Hz) 30024624 R<sub>OUT</sub> vs. Frequency 5\ 100k 1M 10M 100M FREQUENCY (Hz) 30024626

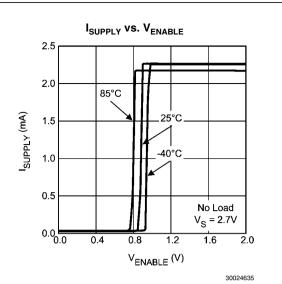

I<sub>SUPPLY</sub> vs. V<sub>SUPPLY</sub>

3.0

5V

-40°C

No Load

Enable<sub>1</sub> =  $V_{DD}$ Enable<sub>2</sub> =  $V_{SS}$

5.0

5.5

30024622

4.5

25 <sup>o</sup>

85°C

4.0

VSUPPLY (V)

3.5

30024630

$\rm I_{SC}$  Sourcing vs.  $\rm V_{SUPPLY}$  Over Temperature

# LMH2180

-40°C 25°C 3.5 .85°C. 3.0 Isupply (mA) 2.5 2.0 1.5 1.0 0.5 No Load V<sub>S</sub> = 5V 0.0 0.0 0.4 0.8 1.2 1.6 2.0 V<sub>ENABLE</sub> (V) 30024636

## **Application Information**

### GENERAL

The LMH2180 is designed to minimize the effects of spurious signals from the base chip to the oscillator. Also the influence of varying load resistance and capacitance to the oscillator is minimized, while the drive capability is increased.

The inputs of the LMH2180 are internally biased at 1V, making AC coupling possible without external bias resistors.

To optimize current consumption, a buffer that is not in use can be disabled by connecting it's enable pin to  $V_{\rm SS}.$

The LMH2180 has no internal ground reference; therefore, either single or split supply configurations can be used.

The LMH2180 is an easy replacement for discrete circuitry. It simplifies board layout and minimizes the effect of layout related parasitic components.

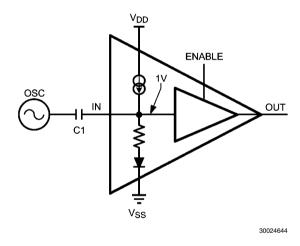

#### INPUT CONFIGURATION

The internal 1V input biasing allows AC coupling of the input signal. This biasing avoids the use of external resistors, as depicted in *Figure 1*. The biasing prevents a large DC load at the oscillators output that creates a load impedance and may affect it's oscillating frequency. As a result of this biasing, the maximum amplitude of the AC signal is  $2V_{\rm PP}$ .

The coupling capacitance C1 should be large enough to let the AC signal pass. This is a unity gain buffer with rail-to-rail inputs and outputs.

FIGURE 1. Input Configuration

#### FREQUENCY PULLING

Frequency pulling is the frequency variation of an oscillator caused by a varying load. In the typical application, the load of the oscillator is a fixed capacitor (C1) in series with the input impedance of the buffer.

To keep the input impedance as constant as possible, the input is biased at 1V, even when the part is disabled. A simplified schematic of the input configuration is shown in *Figure 1*.

### **ISOLATION AND CROSSTALK**

Output to input isolation prevents the clock signal of the oscillator from being affected by spurious signals generated by the digital blocks behind the output buffer. See the characteristic graphic entitled Isolation Output to Input vs. Frequency.

A block diagram of the isolation is shown in *Figure 2*. Crosstalk rejection between buffers prevents signals from affecting each other. *Figure 2* shows a Baseband IC and a Bluetooth module as an example. See the characteristic graphic labeled Crosstalk Rejection vs. Frequency for more information.

FIGURE 2. Isolation Block Diagram

#### DRIVING CAPACITIVE LOADS

Each buffer can drive a capacitive load. Be aware that every capacitor directly connected to the output becomes part of the loop of the buffer. In most applications the load consists of the capacitance of copper tracks and the input capacitance of the application blocks. Capacitance reduces the gain/phase margin and decreases the stability. This leads to peaking in the frequency response and in extreme situations oscillations can occur. To drive a large capacitive load it is recommended to include a series resistor between the buffer and the load capacitor. The best value for this isolation resistance can be found by experimentation.

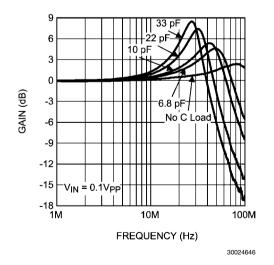

The LMH2180 datasheet reflects measurements with capacitive loads of 10 pF at the output of the buffers. Most common applications will probably use a lower capacitive load, which will result in lower peaking and significantly greater bandwidth, see *Figure 3*.

FIGURE 3. Bandwidth and Peaking

### PHASE NOISE

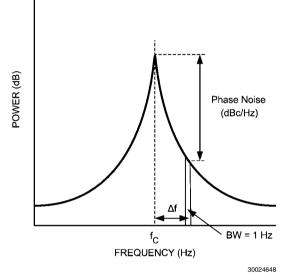

A clock buffer adds noise to the clock signal. This noise causes uncertainty in the phase of the clock signal. This uncertainty is described by jitter (time domain) or phase noise (frequency domain). Communication systems, such as Wireless LAN, require a low jitter/phase noise clock signal to obtain a low Bit Error Rate. *Figure 4* shows the frequency domain representation of a clock signal with frequency f<sub>C</sub>. Without Phase Noise the entire signal power would only be located at the frequency f<sub>C</sub>. Phase Noise spreads some of the power to adjacent frequencies. Phase Noise is usually specified in dBc/Hz at a given frequency offset  $\Delta f$  from the carrier, where dBc is the power level in dB relative to the carrier. The noise power is measured within a 1 Hz bandwidth.

FIGURE 4. Phase Noise

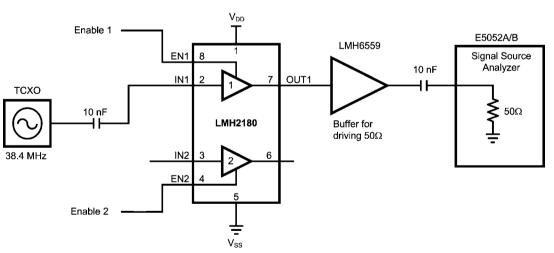

*Figure 5* shows the setup used to measure the LMH2180 phase noise. The clock driving the LMH2180 is a state of the art 38.4MHz TCXO. Both the TCXO phase noise and the phase noise at the LMH2180 output were measured. At offset frequencies of 1 kHz and higher from the carrier, the TCXO phase noise is sufficiently low to accurately calculate the LMH2180 contribution to the phase noise at the output. The LMH6559, whose phase noise contribution can be neglected, is used to drive the  $50\Omega$  input impedance of the Signal Source Analyzer.

### LAYOUT DESIGN RECOMMENDATION

Careful consideration during circuit design and PCB layout will eliminate problems and will optimize the performance of the LMH2180. It is best to have the same ground plane on the PCB for all decoupling and other ground connections.

To ensure a clean supply voltage it is best to place decoupling capacitors close to the LMH2180, between  $V_{\rm DD}$  and  $V_{\rm SS}.$

Another important issue is the value of the components, because this also determines the sensitivity to disturbances. Resistor values have to be low enough to avoid a significant noise contribution and large enough to avoid a significant increase in power consumption while loading inputs or outputs to heavily.

30024647

FIGURE 5. Measurement Setup

## Physical Dimensions inches (millimeters) unless otherwise noted

LMH2180

## Notes

| Pr                             | oducts                       | De                      | sign Support                   |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com